# A System-On-Chip Radiation Hardened Microcontroller ASIC With Embedded SpaceWire Router

Richard Berger, Laura Burcin, David Hutcheson, Jennifer Koehler, Marla Lassa, Myrna Milliser, David Moser, Dan Stanley, Randy Zeger, Ben Blalock, Mark Hale

## **International SpaceWire Conference 2007**

# **Introduction / Project Goals**

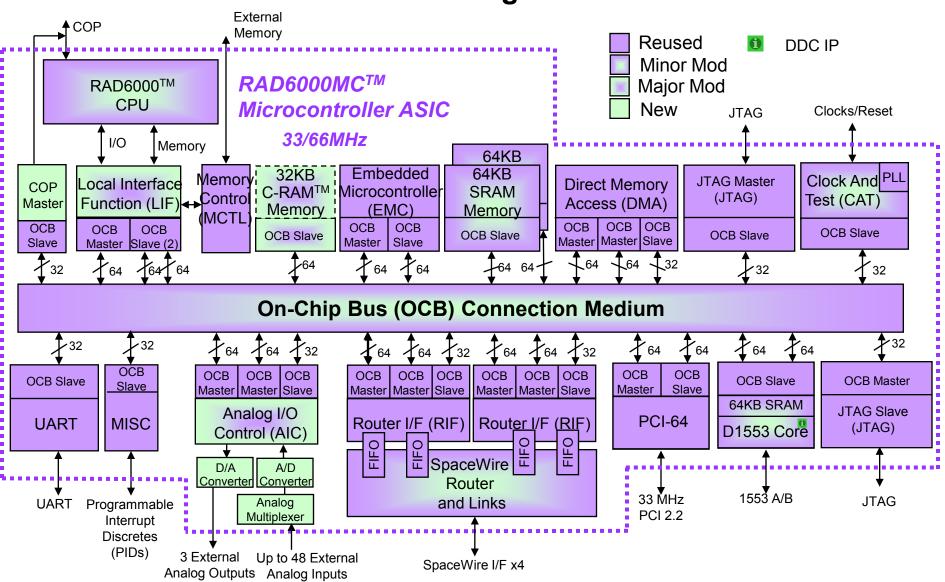

- The RAD6000MC<sup>™</sup> microcontroller is being designed to consolidate all the key elements needed for moderate levels of spaceborne computing into a single ASIC

- It is flexible enough for a wide variety of applications, from instrument control to "safe mode" back-up

- The RAD6000MC will be manufactured in BAE Systems' RH15 150nm radiation hardened technology, with a goal of 10x improvement in powerperformance vs. existing RAD600-based single board computers

- Based on the space-proven RAD6000 CPU, it will include strong software support for users

- Green Hills Compiler

- VxWorks operating system with possible addition of real time embedded solution as well

- Easy reuse/migration of existing RAD6000 application code

- Reuse of existing RAD6000 infrastructure

# RAD6000MC<sup>™</sup> Features

### Planned Radiation Characteristics

- Total Dose: 1Mrad (Si)

- Single Event Effects

- <1E-10 errors/bit-day</li>

- Latch-up immune

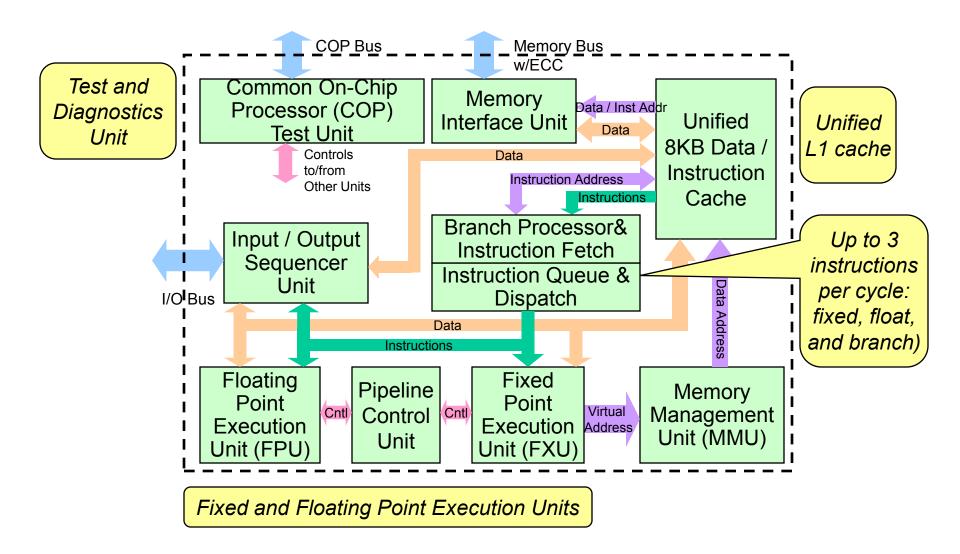

### Processor Units

- RAD6000™ CPU

- Selectable 33 or 66 MHz clock

- Fixed and floating point execution units

- Up to 3 instructions/cycle

- 8KB unified D/I cache

- Embedded Microcontroller (EMC)

### SRAM and Non-volatile Memory with controllers

- 128 KB synchronous SRAM on-chip memory

- 32 KB C-RAM™ non-volatile program store

- External Memory controller for SRAM, DRAM, C-RAM, etc.

- Direct Memory Access (DMA) controller

### I/O Bus and Communications Interfaces

- 33 MHz, 64-bit PCI interface (version 2.2)

- 16550 compatible UART

- SpaceWire router with 4 serial links

- Dual 1553 interface w/64 KB of on-chip SRAM

### JTAG master and slave test controllers

### Analog interfaces

- 12-bit, 8.25 Msps A-D converter

- 48 input programmable analog multiplexer

- Three 12-bit 1 Ksps D-A converters

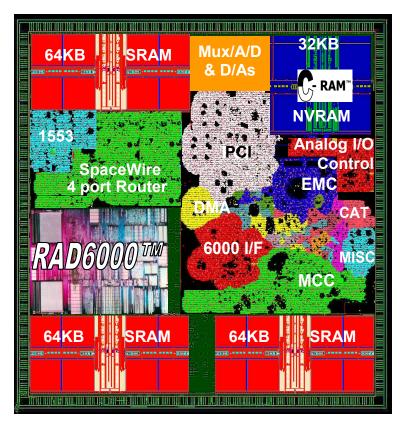

# **RAD6000MC ASIC Block Diagram**

**BAE SYSTEMS**

# **RAD6000 Microprocessor**

### **Local Interface Function (LIF) Block Diagram** BAE SYSTEMS RAD6000 RAD6000 I/O Bus **Memory Bus** Wrap feature supports use of on-chip Start-up ROM using the C-RAM PIO **RAD6000** DMA core I/F Memory I/F I/F Memory Memory Controller Request **Contains Base** Request Address I/F Bus Configuration Registers used for Address Registers Memory Memory Translation, to Controller Configuration extend RAD6000 MC Bus I/F 27-bit (128 MB) address to 4 GB Additional slave **OCB Slave OCB Master OCB Slave** OCB interface supports direct (0) I/FI/F (1) I/F access to external

memory from other on-chip cores

OCB Slave (1) Stub

OCB Slave (0) Stub

**OCB Master Stub**

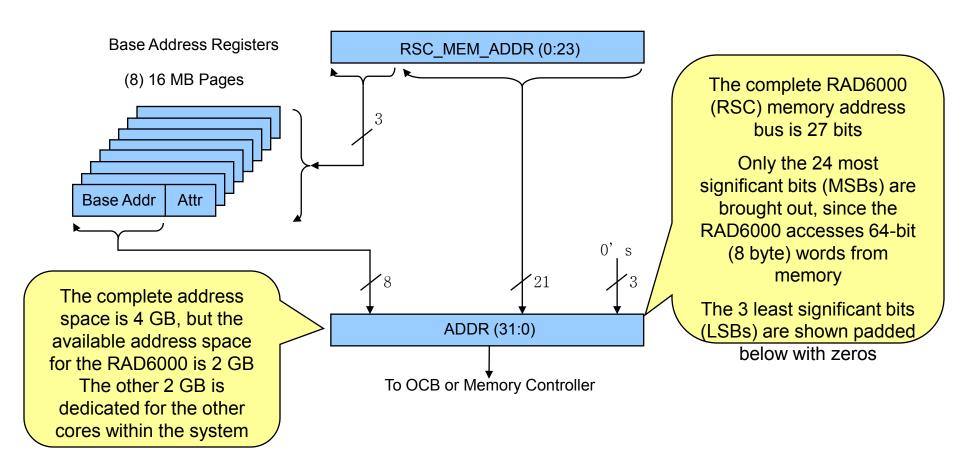

# **RAD6000 Memory Address Translation**

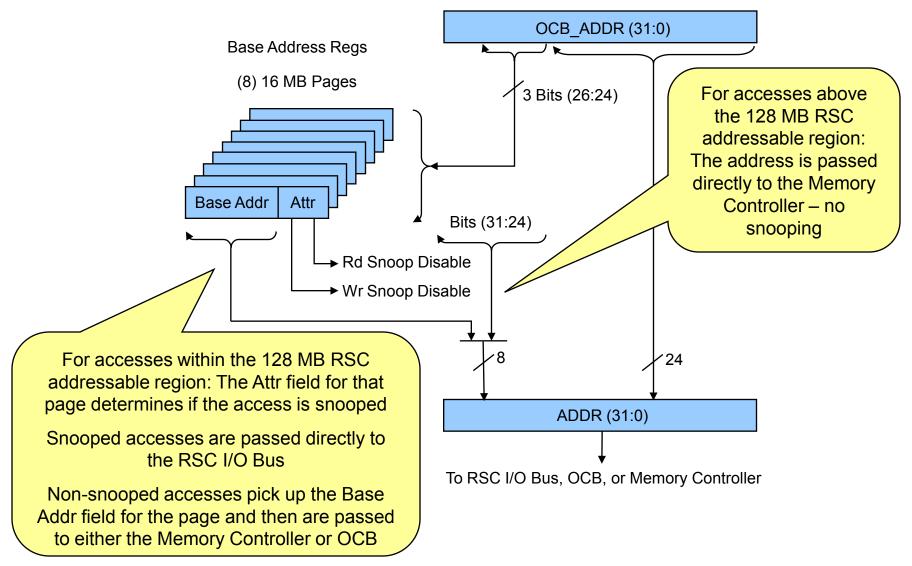

# On-Chip Bus Slave Memory Address Translation

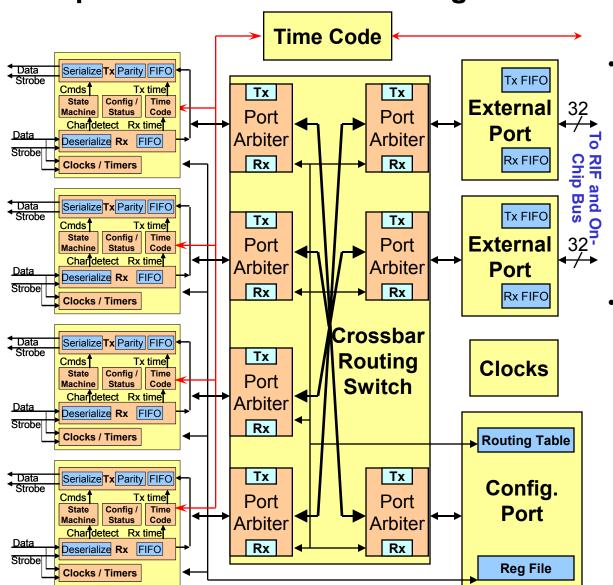

# **SpaceWire Router Block Diagram and Features**

- SpaceWire core implementation

- Four SpaceWire ports include integrated LVDS drivers / receivers with support for cold sparing

- Dual ports connected to On-Chip Bus increase throughput

- 350 MHz maximum data rate on SpaceWire link interfaces

- Unique switch enhancements

- Bypass Mode ignores

SpaceWire addressing and fixes route assignment for packet

- Local header byte indicates port # received from and presence of Logical Address

- Network blockage mitigation by limiting packet length limits risk of network stalling

# **Programmable Multiplexer and A/D Converter**

| All (48)        | 32 Single<br>Ended    | 16 Single<br>Ended | All (24)     |

|-----------------|-----------------------|--------------------|--------------|

| Single<br>Ended |                       | and 16             | Differential |

| Inputs          | And 8<br>Differential | Differential       | Inputs       |

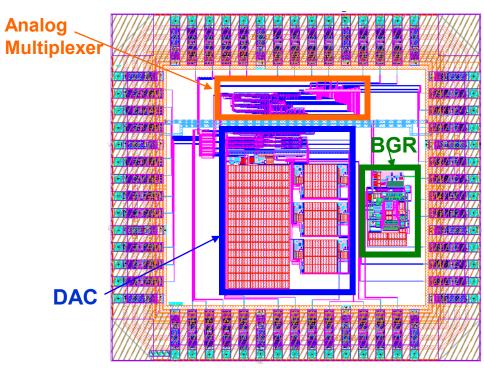

- Analog Multiplexer with programmable input configurations, supporting singleended, differential, or mixed input signals

- Select signals controlled from Analog I/O Control digital core

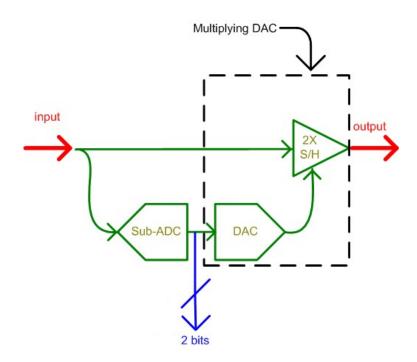

- 12-bit Pipeline A/D converter with 1.5 bits per stage (single stage shown)

- High performance Sample and Hold circuit with Operational Transconductance Amplifiers

- Digital error correction tolerates 500 mV of comparator offset

- Supported by Bandgap Reference circuit to generate differential reference voltage

# Wilkinson Architecture Three Channel D/A Converter

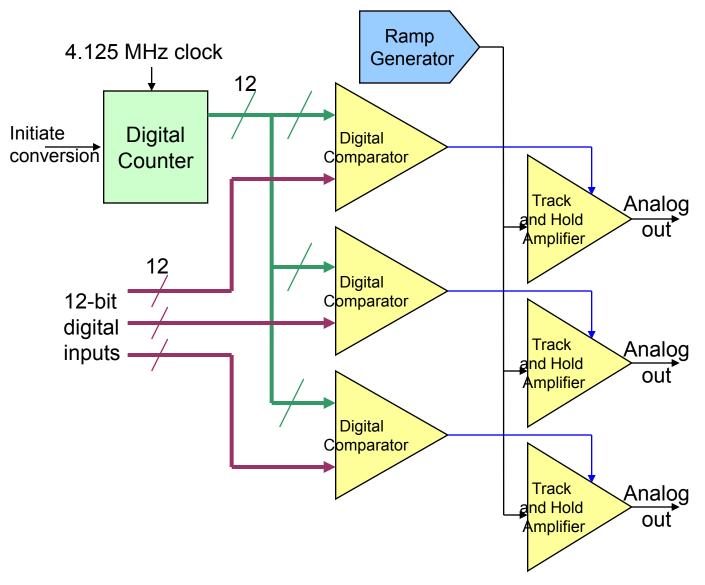

- Wilkinson D/A converter architecture

- Shared ramp generator and digital counter

- Repeated comparators and track and hold amps

- Pipelined gray code digital counter uses

4,096 cycles for 12 bit resolution @ 1 Ksps

- Track and Hold samples ramp voltage when comparator pulses

- Minimal die and power dissipation for low speed conversion

# **Analog Circuit Test Chips**

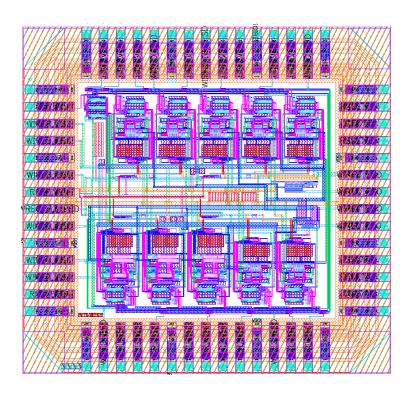

Pipeline A/D Converter test chip

Wilkinson D/A Converter, analog multiplexer, and Bandgap Reference test chip

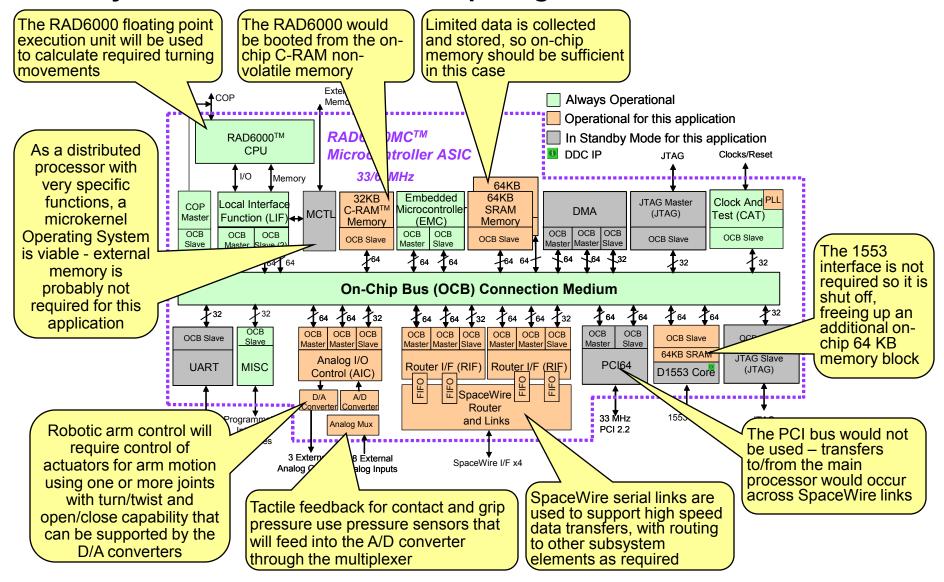

# Example Application – Robotic Arm Control on a System With Distributed Computing

**BAE SYSTEMS**

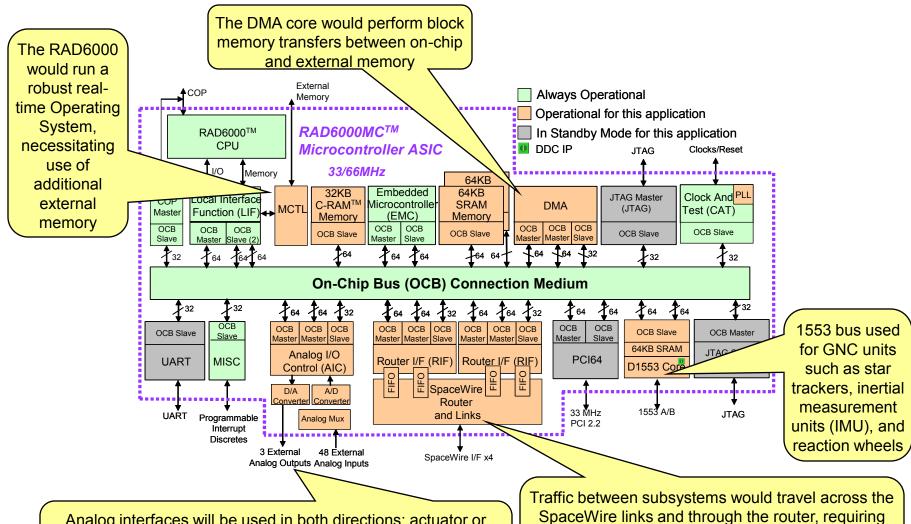

# **Example Application – Small Satellite Flight Computer**

BAE SYSTEMS

Analog interfaces will be used in both directions: actuator or thruster control (D/A) and sensor health monitoring (multiplexed A/D), with the EMC assisting in management of collected sensor data to memory

SpaceWire links and through the router, requiring operation of the PLL associated with the serial links and the EMC used to control transfers between the router and on-chip memory blocks

# Summary

- The RAD6000MC is a flexible microcontroller supported by a robust set of digital and analog interfaces

- A redundant MIL-STD-1553 is provided, with embedded SRAM that can be used elsewhere if the interface is not used

- A SpaceWire router with 4 serial links and dual internal ports is provided for high speed transfer with minimal connections

- A 64-bit PCI interface offers increased parallel bus throughput

- Analog/Digital conversion is supported by a programmable multiplexer

- A novel approach was employed to achieve multiple channels of Digital/Analog conversion with very low power dissipation

- Enhancements have been made to address previous limitations in the RAD6000 microprocessor's addressable memory space

- The ASIC is built around a reusable core architecture and heavily leverages reuse of validated and flight proven designs

- RAD6000MC configuration can be matched to user applications, optimizing features and power dissipation